Data Sheet, May 2000

mining

## C504 8-Bit Single-Chip Microcontroller

### Microcontrollers

Never stop thinking.

Edition 2000-05

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2000. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# C504 8-Bit Single-Chip Microcontroller

## Microcontrollers

Never stop thinking.

#### C504

| <b>Revision History:</b> |                                            | 2000-05                               |

|--------------------------|--------------------------------------------|---------------------------------------|

| Previous V               | ersion:                                    | 1996-05                               |

| Page Subjects (m         |                                            | ajor changes since last revision)     |

| 35 - 40                  | OTP Memory Operation is added.             |                                       |

| 41                       | Table on Vei                               | rsion Byte Content is added.          |

| 57 - 60                  | AC Characte                                | ristics of Programming Mode is added. |

| several                  | $V_{\rm CC}$ is replaced by $V_{\rm DD}$ . |                                       |

| several                  | Specification                              | for SAH-C504 is removed               |

Enhanced Hooks Technology<sup>TM</sup> is a trademark and patent of Metalink Corporation licensed to Infineon Technologies.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

#### 8-Bit Single-Chip Microcontroller C500 Family

#### C504

- Fully compatible to standard 8051 microcontroller

- Up to 40 MHz external operating frequency

- 16 Kbyte on-chip program memory

- C504-2R: ROM version (with optional ROM protection)

- C504-2E: programmable OTP version

- C504-L: without on-chip program memory

- 256 byte on-chip RAM

- 256 byte on-chip XRAM

- Four 8-bit ports

- 2 ports with mixed analog/digital I/O capability

- Three 16-bit timers/counters

- Timer 2 with up/down counter feature

Further features are listed next page.

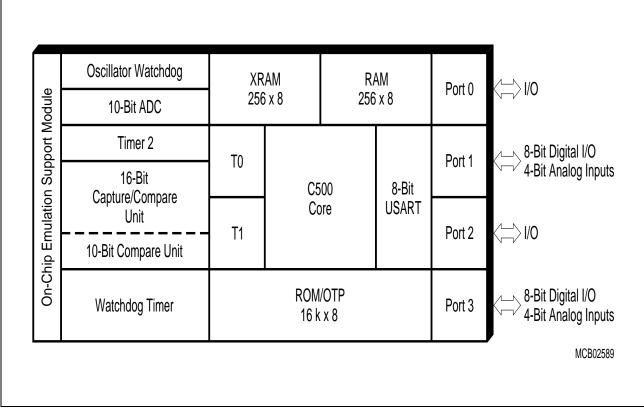

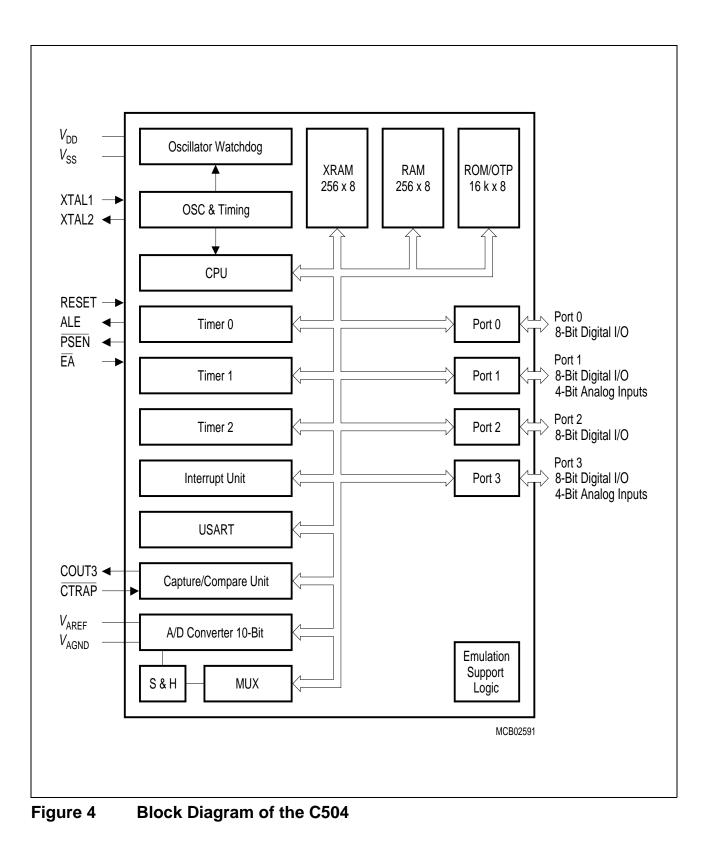

#### Figure 1 C504 Functional Units

C504

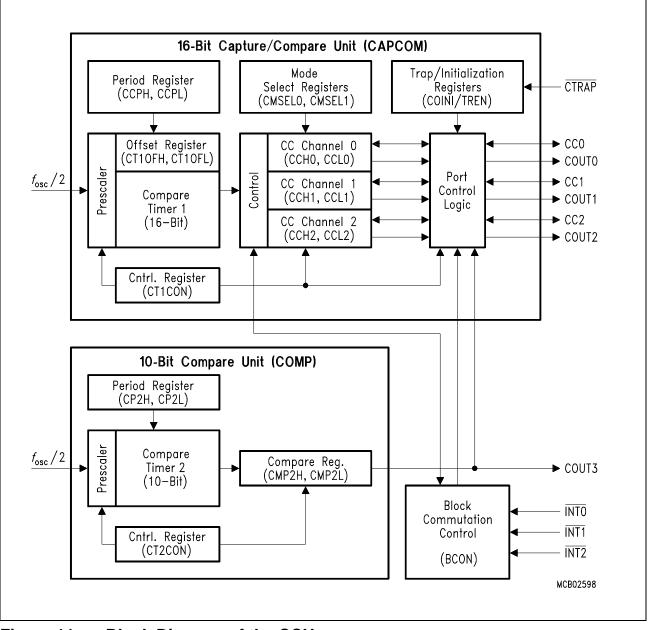

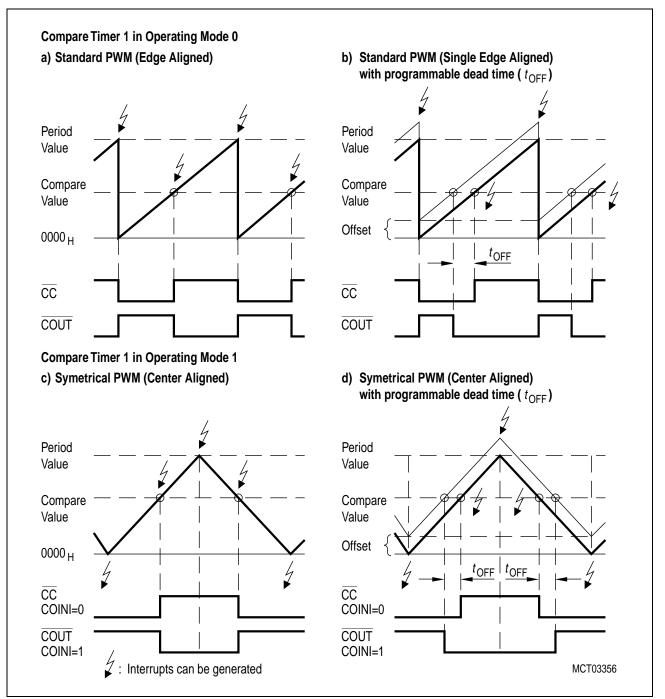

- Capture/compare unit for PWM signal generation and signal capturing

- 3-channel, 16-bit capture/compare unit

- 1-channel, 10-bit compare unit

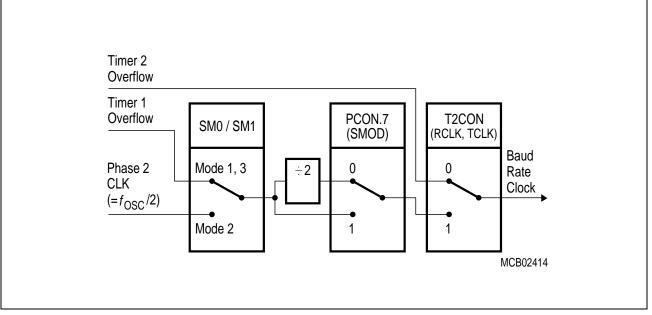

- Full duplex serial interface (USART)

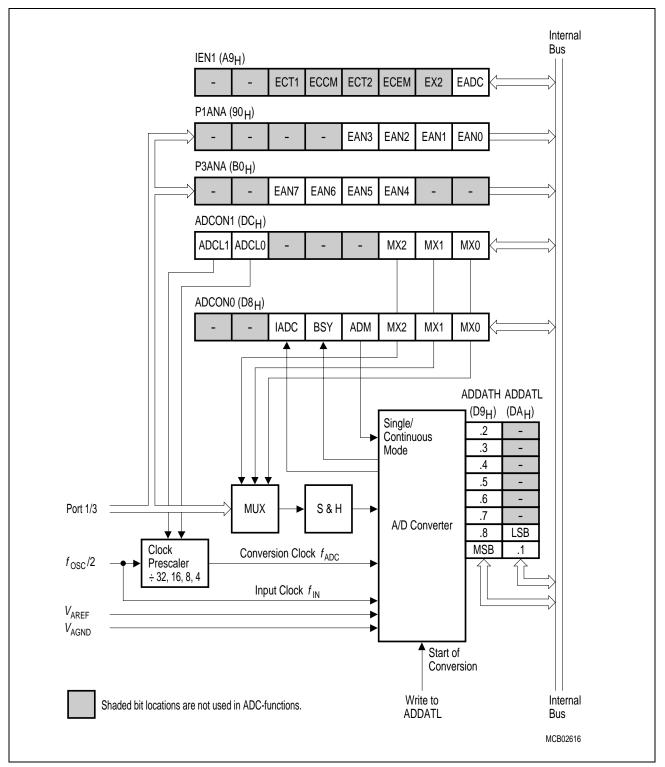

- 10-bit A/D Converter with 8 multiplexed inputs

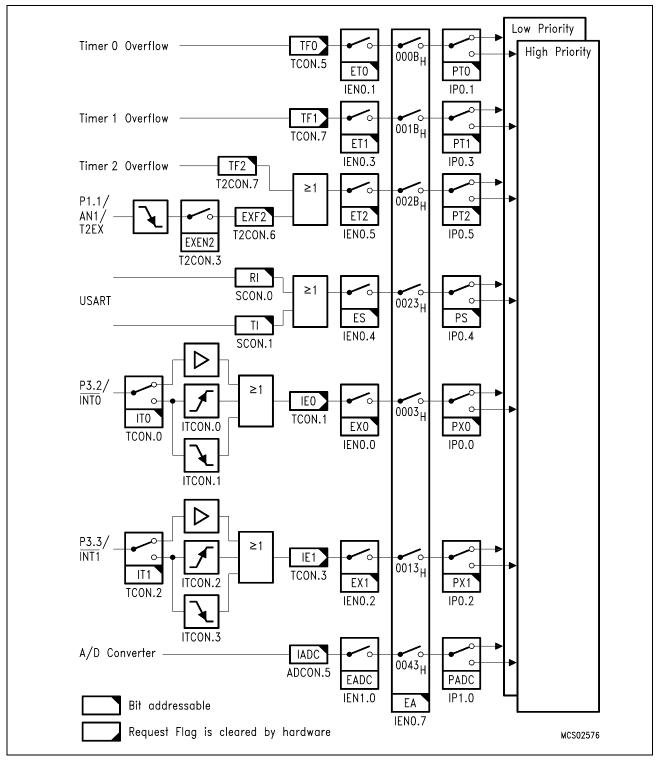

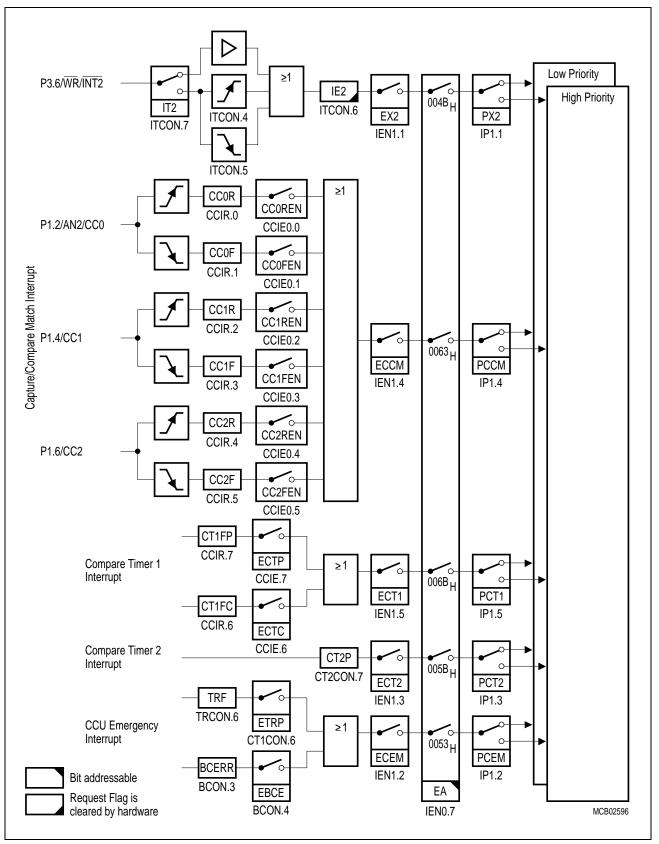

- · Twelve interrupt sources with two priority levels

- On-chip emulation support logic (Enhanced Hooks Technology™)

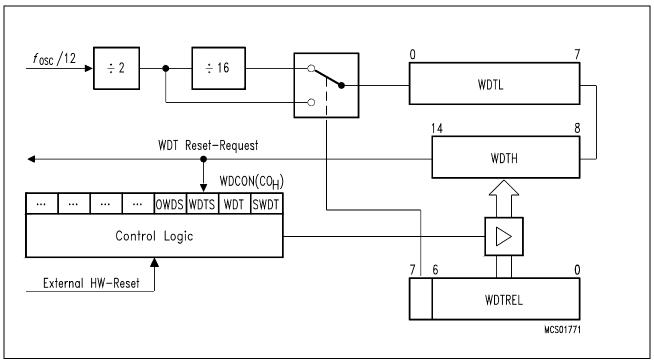

- Programmable 15-bit Watchdog Timer

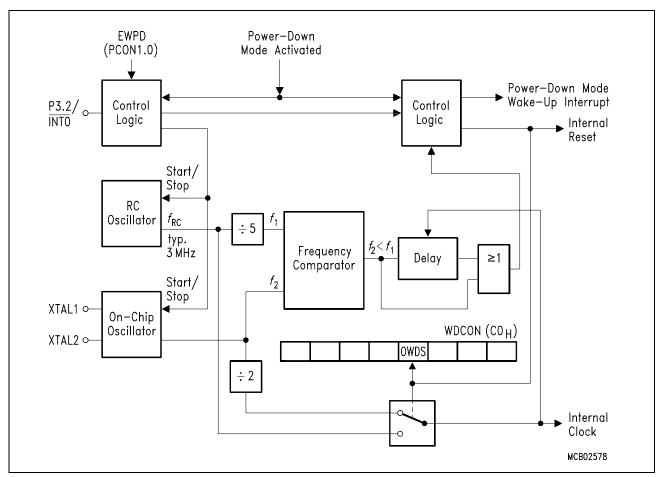

- Oscillator Watchdog

- Fast Power On Reset

- Power Saving Modes

- Idle mode

- Power-down mode with wake-up capability through INTO

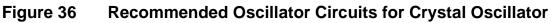

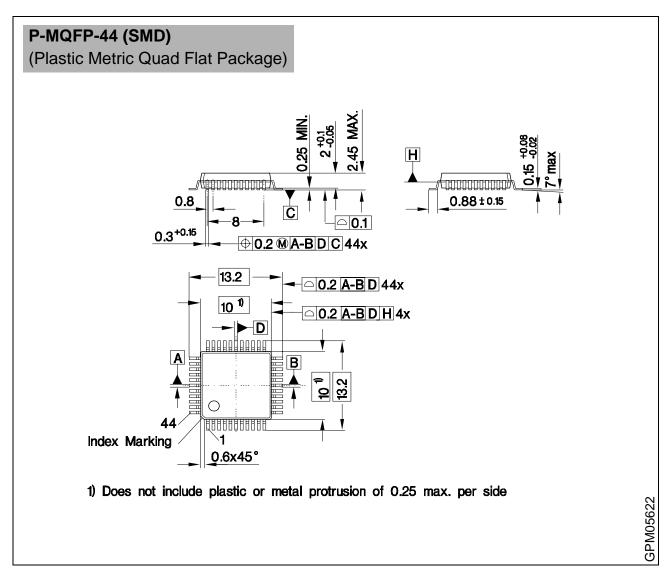

- M-QFP-44 package

- Temperature ranges: SAB-C504  $T_A$ :

- SAB-C504

$T_A$ :

0 to 70 °C

SAF-C504

$T_A$ :

40 to 85 °C

SAK-C504

$T_A$ :

40 to 125 °C

(max. operating frequency: 24 MHz)

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code indentifies:

- The derivative itself, i.e. its function set

- the specified temperature range

- the package and the type of delivery

For the available ordering codes for the C504, please refer to the "**Product Information Microcontrollers**" which summarizes all available microcontroller variants.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

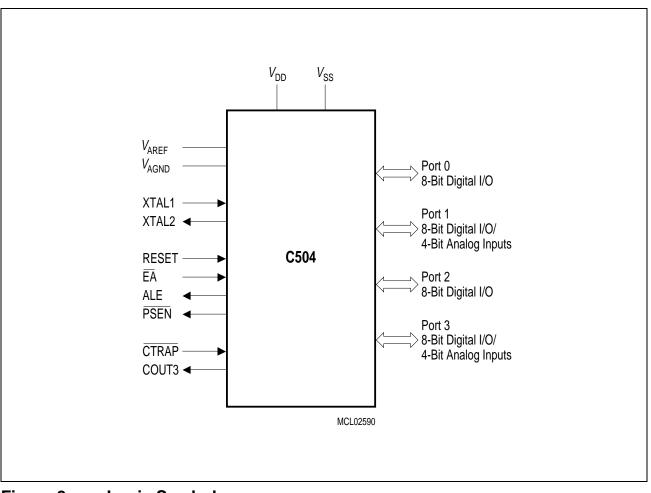

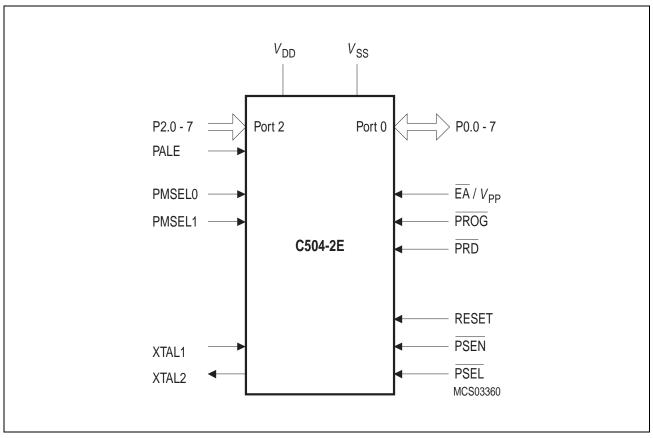

Figure 2 Logic Symbol

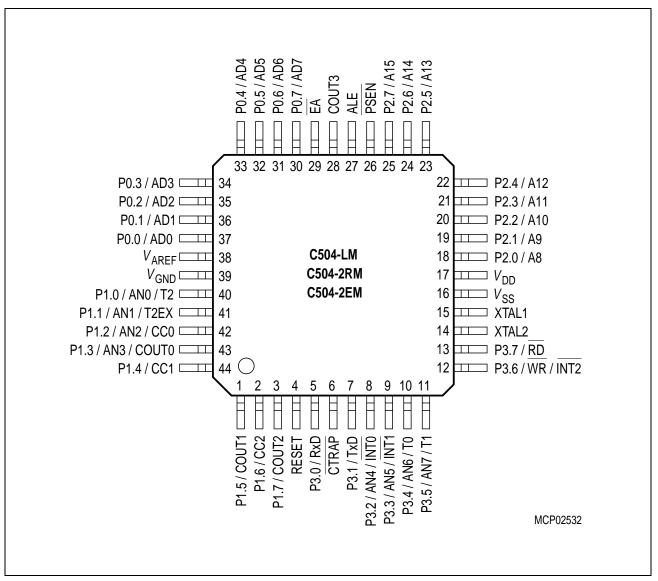

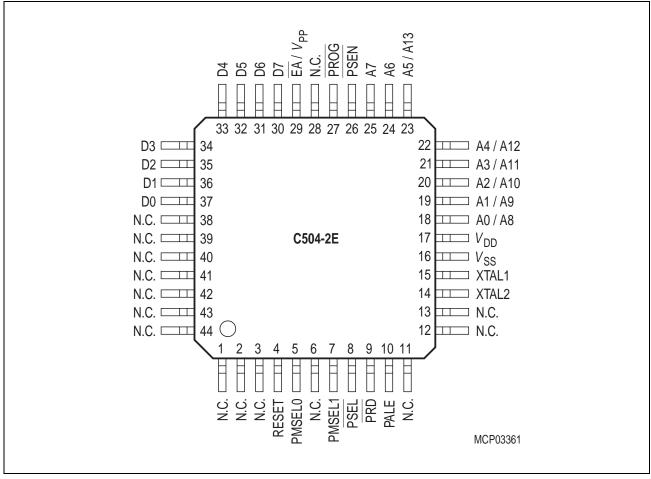

Figure 3Pin Configuration (top view)

| Table 1 | <b>Pin Definitions and Functions</b> |

|---------|--------------------------------------|

|         |                                      |

| Symbol      | Pin Number<br>(P-MQFP-44) | I/O <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                           |                                                                                |  |  |  |  |

|-------------|---------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| P1.0 - P1.7 | 40 - 44,<br>1 - 3         | I/O               | <b>Port 1</b><br>is an 8-bit bidirectional port. Port 1 pins can be used                                                                                                                                                                                                                           |                                                                                |  |  |  |  |

|             |                           |                   | for digital input/output. P1.0 - P1.3 can also be used<br>as analog inputs of the A/D converter. As secondary<br>digital functions, Port 1 contains the Timer 2 pins<br>and the Capture/Compare inputs/outputs. Port 1<br>pins are assigned to be used as analog inputs via<br>the register P1ANA. |                                                                                |  |  |  |  |

|             |                           |                   | The functions are as follows:                                                                                                                                                                                                                                                                      | signed to the pins of Port 1 as                                                |  |  |  |  |

|             | 40                        |                   | P1.0 / AN0 / T2                                                                                                                                                                                                                                                                                    | Analog input channel 0 /<br>input to Timer 2                                   |  |  |  |  |

|             | 41                        |                   | P1.1 / AN1 / T2EX                                                                                                                                                                                                                                                                                  | Analog input channel 1 /<br>capture/reload trigger of Timer<br>2 up-down count |  |  |  |  |

|             | 42                        |                   | P1.2 / AN2 / CC0                                                                                                                                                                                                                                                                                   | Analog input channel 2 /<br>input/output of capture/<br>compare channel 0      |  |  |  |  |

|             | 43                        |                   | P1.3 / AN3 / COUT0                                                                                                                                                                                                                                                                                 | Analog input channel 3 /<br>output of capture/compare<br>channel 0             |  |  |  |  |

|             | 44                        |                   | P1.4 / CC1                                                                                                                                                                                                                                                                                         | Input/output of capture/<br>compare channel 1                                  |  |  |  |  |

|             | 1                         |                   | P1.5 / COUT1                                                                                                                                                                                                                                                                                       | Output of capture/compare channel 1                                            |  |  |  |  |

|             | 2                         |                   | P1.6 / CC2                                                                                                                                                                                                                                                                                         | Input/output of capture/<br>compare channel 2                                  |  |  |  |  |

|             | 3                         |                   | P1.7 / COUT2                                                                                                                                                                                                                                                                                       | Output of capture/compare channel 2                                            |  |  |  |  |

| RESET       | 4                         | 1                 | <b>RESET</b><br>A high level on this pin for two machine cycles where the oscillator is running resets the device. An internal diffused resistor to $V_{SS}$ permits power-on reset using only an external capacitor to $V_{DD}$ .                                                                 |                                                                                |  |  |  |  |

| Symbol      | Pin Number<br>(P-MQFP-44) | I/O <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                          |  |  |  |  |

|-------------|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P3.0 - P3.7 | 5, 7 - 13                 | I/O               | <b>Port 3</b><br>is an 8-bit bidirectional port. P3.0 (R×D) and P3.1<br>(T×D) operate as defined for the C501. P3.2 to P3.7<br>contain the external interrupt inputs, timer inputs,<br>and four of the analog inputs of the A/D converter.<br>Port 3 pins are assigned to be used as analog inputs<br>via the bits of SFR P3ANA. P3.6/WR can be<br>assigned as a third interrupt input. |                                                                                                                          |  |  |  |  |

|             |                           |                   | The functions are a follows:                                                                                                                                                                                                                                                                                                                                                            | assigned to the pins of port 3 as                                                                                        |  |  |  |  |

|             | 5                         |                   | P3.0 / RxD                                                                                                                                                                                                                                                                                                                                                                              | Receiver data input (asynch.) or<br>data input/output (synch.) of<br>serial interface                                    |  |  |  |  |

|             | 7                         |                   | P3.1 / TxD                                                                                                                                                                                                                                                                                                                                                                              | Transmitter data output<br>(asynch.) or clock output<br>(synch.) of serial interface                                     |  |  |  |  |

|             | 8                         |                   | P3.2 / AN4 / INTO                                                                                                                                                                                                                                                                                                                                                                       | Analog input channel 4 /<br>external interrupt 0 input /<br>Timer 0 gate control input                                   |  |  |  |  |

|             | 9                         |                   | P3.3 / AN5 / INT1                                                                                                                                                                                                                                                                                                                                                                       | Analog input channel 5 /<br>external interrupt 1 input /<br>Timer 1 gate control input                                   |  |  |  |  |

|             | 10                        |                   | P3.4 / AN6 / T0                                                                                                                                                                                                                                                                                                                                                                         | Analog input channel 6 / Timer 0<br>counter input                                                                        |  |  |  |  |

|             | 11                        |                   | P3.5 / AN7 / T1                                                                                                                                                                                                                                                                                                                                                                         | Analog input channel 7 / Timer 1<br>counter input                                                                        |  |  |  |  |

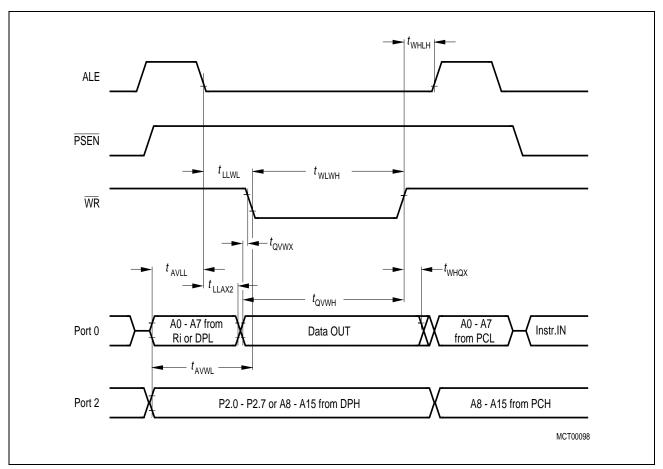

|             | 12                        |                   | P3.6 / WR / INT2                                                                                                                                                                                                                                                                                                                                                                        | WR control output; latches the<br>data byte from port 0 into the<br>external data memory /<br>external interrupt 2 input |  |  |  |  |

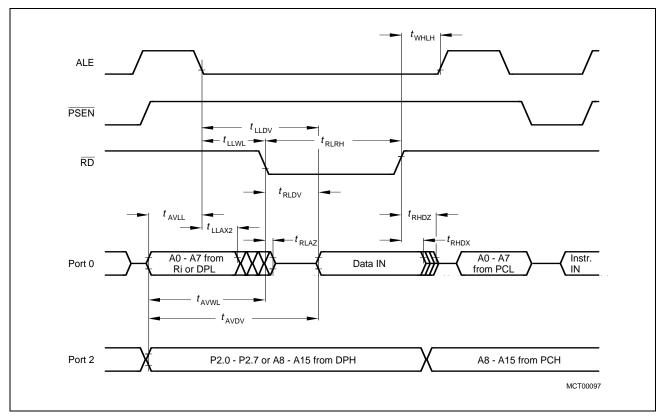

|             | 13                        |                   | P3.7 / RD                                                                                                                                                                                                                                                                                                                                                                               | RD control output; enables the external data memory                                                                      |  |  |  |  |

| Symbol      | Pin Number<br>(P-MQFP-44) | <b>I/O</b> <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTRAP       | 6                         | 1                        | <b>CCU</b> <u><b>Trap Input</b></u><br>With CTRAP = low, the compare outputs of the<br>CAPCOM unit are switched to the logic level as<br>defined in the COINI register (if they are enabled by<br>the bits in SFR TRCON). CTRAP is an input pin with<br>an internal pullup resistor. For power saving<br>reasons, the signal source which drives the CTRAP<br>input should be at high or floating level during<br>power-down mode.                                                                                                                                                                                                                                                                                                                                                                                          |

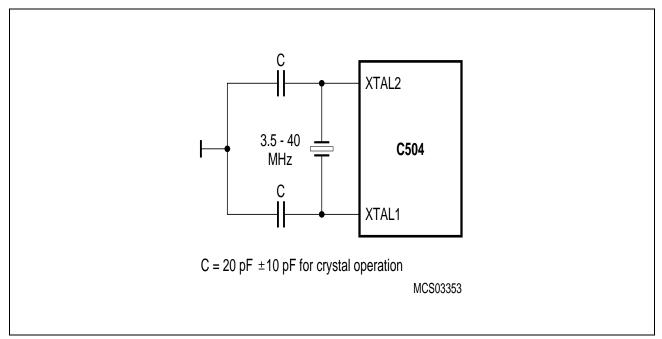

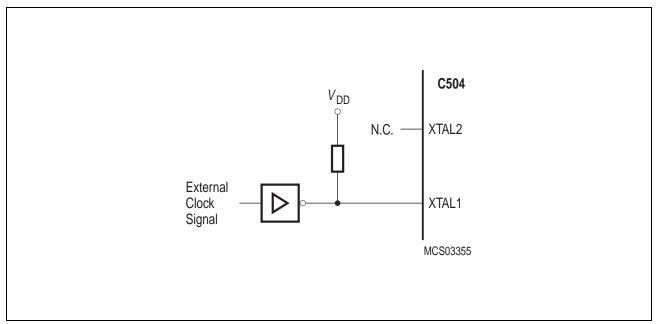

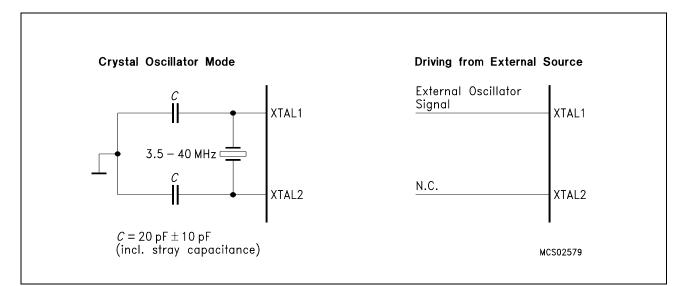

| XTAL2       | 14                        | _                        | <b>XTAL2</b><br>Output of the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

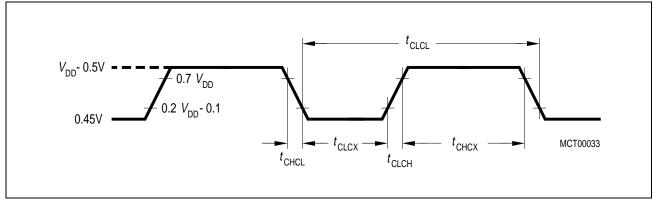

| XTAL1       | 15                        | -                        | XTAL1<br>Input to the inverting oscillator amplifier and input to<br>the internal clock generator circuits.<br>To drive the device from an external clock source,<br>XTAL1 should be driven, while XTAL2 is left<br>unconnected. There are no requirements on the<br>duty cycle of the external clock signal, since the<br>input to the internal clocking circuitry is divided down<br>by a divide-by-two flip-flop. Minimum and maximum<br>high and low times as well as rise/fall times specified<br>in the AC characteristics must be observed.                                                                                                                                                                                                                                                                          |

| P2.0 - P2.7 | 18-25                     | I/O                      | <b>Port 2</b><br>is a bidirectional I/O port with internal pullup<br>resistors. Port 2 pins that have "1"s written to them<br>are pulled high by the internal pullup resistors, and<br>in that state can be used as inputs. As inputs, Port 2<br>pins being externally pulled low will source current<br>( $I_{IL}$ , in the DC characteristics) because of the<br>internal pullup resistors. Port 2 emits the high-order<br>address byte during fetches from external program<br>memory and during accesses to external data<br>memory that use 16-bit addresses (MOVX @DPTR).<br>In this application it uses strong internal pullup<br>resistors when issuing "1"s. During accesses to<br>external data memory that use 8-bit addresses<br>(MOVX @Ri), Port 2 issues the contents of the P2<br>special function register. |

### Table 1Pin Definitions and Functions (cont'd)

| Symbol      | Pin Number<br>(P-MQFP-44) | I/O <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------|---------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

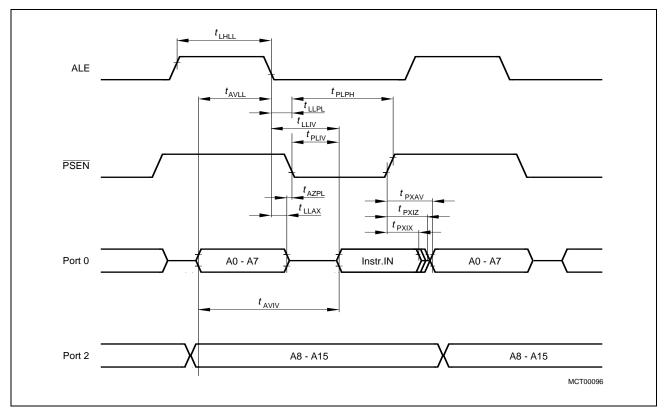

| PSEN        | 26                        | 0                 | The <b>Program Store Enable</b><br>output is a control signal that enables the external<br>program memory to the bus during external fetch<br>operations. It is activated every six oscillator periods<br>except during external data memory accesses.<br>Remains high during internal program execution.                                                                                                                                                                                                                                                          |  |  |  |  |

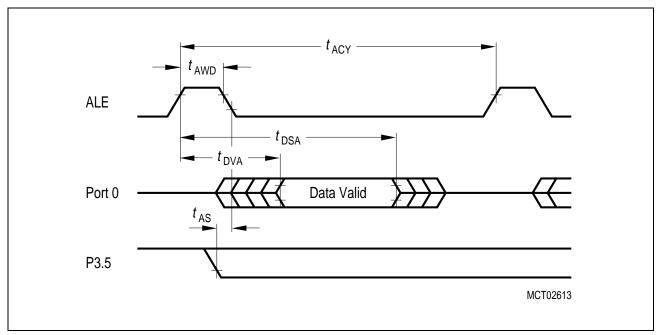

| ALE         | 27                        | Ο                 | The Address Latch Enable<br>output is used for latching the low-byte of the<br>address into external memory during normal<br>operation. It is activated every six oscillator periods<br>except during an external data memory access.<br>When instructions are executed from internal ROM<br>$(\overline{EA} = 1)$ the ALE generation can be disabled by<br>clearing bit EALE in SFR SYSCON.                                                                                                                                                                       |  |  |  |  |

| COUT3       | 28                        | 0                 | <b>10-Bit compare channel output</b><br>This pin is used for the output signal of the 10-bit<br>Compare Timer 2 unit. COUT3 can be disabled and<br>set to a high or low state.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| ĒĀ          | 29                        | 1                 | <b>External Access Enable</b><br>When held at high level, instructions are fetched<br>from the internal ROM (C504-2R only) when the PC<br>is less than 4000 <sub>H</sub> . When held at low level, the C504<br>fetches all instructions from external program<br>memory.<br>For the C504-L, this pin must be tied low.                                                                                                                                                                                                                                             |  |  |  |  |

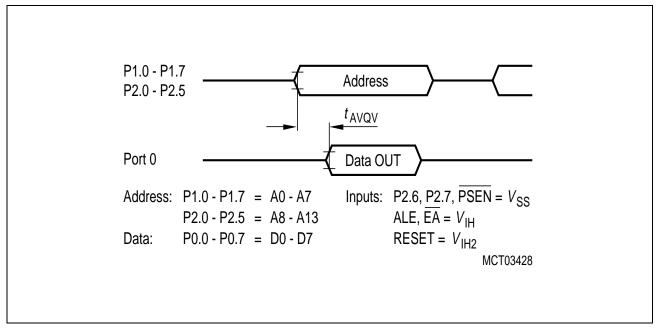

| P0.0 - P0.7 | 37 - 30                   | I/O               | <b>Port 0</b><br>is an 8-bit open-drain bidirectional I/O port. Port 0<br>pins that have "1"s written to them float; and in that<br>state, can be used as high-impedance inputs. Port 0<br>is also the multiplexed low-order address and data<br>bus during accesses to external program or data<br>memory. In this application, it uses strong internal<br>pullup resistors when issuing "1" s.<br>Port 0 also outputs the code bytes during program<br>verification in the C504-2R. External pullup resistors<br>are required during program (ROM) verification. |  |  |  |  |

| $V_{AREF}$  | 38                        | —                 | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

### Table 1Pin Definitions and Functions (cont'd)

| Symbol          | Pin Number<br>(P-MQFP-44) | I/O <sup>1)</sup> | Function                                |

|-----------------|---------------------------|-------------------|-----------------------------------------|

| $V_{AGND}$      | 39                        | -                 | Reference ground for the A/D converter. |

| V <sub>SS</sub> | 16                        | -                 | Ground (0 V)                            |

| $V_{DD}$        | 17                        | _                 | Power Supply (+ 5 V)                    |

1) I = Input,

O = Output

#### CPU

The C504 is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% three-byte instructions. With a 12 MHz crystal, 58% of the instructions are executed in 1.0  $\mu$ s (24 MHz: 500 ns, 40 MHz: 300 ns).

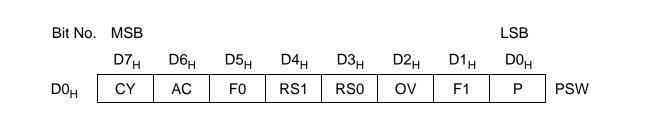

Special Function Register PSW (Address D0<sub>H</sub>)

| Bit        | Functior             | า                                                                                                         |                                                                                    |  |  |  |  |

|------------|----------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| СҮ         | Carry Fla<br>Used by | •                                                                                                         | c instructions.                                                                    |  |  |  |  |

| AC         | -                    | <b>/ Carry F</b><br>instructio                                                                            | lag<br>ns which execute BCD operations.                                            |  |  |  |  |

| F0         | General              | Purpose                                                                                                   | Flag 0                                                                             |  |  |  |  |

| RS1<br>RS0 | •                    | <b>Register Bank Select Control bits</b><br>These bits are used to select one of the four register banks. |                                                                                    |  |  |  |  |

|            | RS1                  | RS0                                                                                                       | Function                                                                           |  |  |  |  |

|            | 0                    | 0                                                                                                         | Bank 0 selected, data address 00 <sub>H</sub> -07 <sub>H</sub>                     |  |  |  |  |

|            | 0                    | 1                                                                                                         | Bank 1 selected, data address 08 <sub>H</sub> -0F <sub>H</sub>                     |  |  |  |  |

|            | 1                    | 0                                                                                                         | Bank 2 selected, data address 10 <sub>H</sub> -17 <sub>H</sub>                     |  |  |  |  |

|            | 1                    | 1                                                                                                         | Bank 3 selected, data address 18 <sub>H</sub> -1F <sub>H</sub>                     |  |  |  |  |

| OV         | Overflov<br>Used by  | •                                                                                                         | c instruction.                                                                     |  |  |  |  |

| F1         | General              | Purpose                                                                                                   | Flag 1                                                                             |  |  |  |  |

| P          |                      | ed by har                                                                                                 | rdware after each instruction to indicate an odd/<br>one" bits in the accumulator. |  |  |  |  |

**Reset Value: 00**<sub>H</sub>

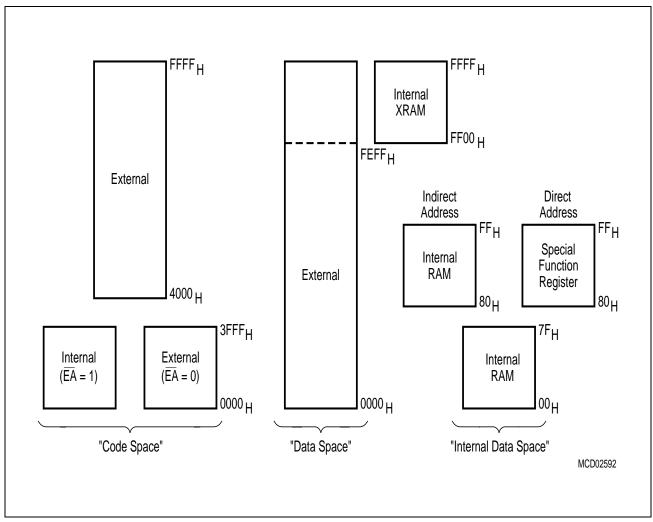

#### **Memory Organization**

The C504 CPU manipulates operands in the following four address spaces:

- up to 64 Kbyte of program memory: 16K ROM for C504-2R

16K OTP for C504-2E

- up to 64 Kbyte of external data memory

- 256 bytes of internal data memory

- 256 bytes of internal XRAM data memory

- a 128 byte special function register area

Figure 5 illustrates the memory address spaces of the C504.

Figure 5 C504 Memory Map

C504

#### **Reset and System Clock Operation**

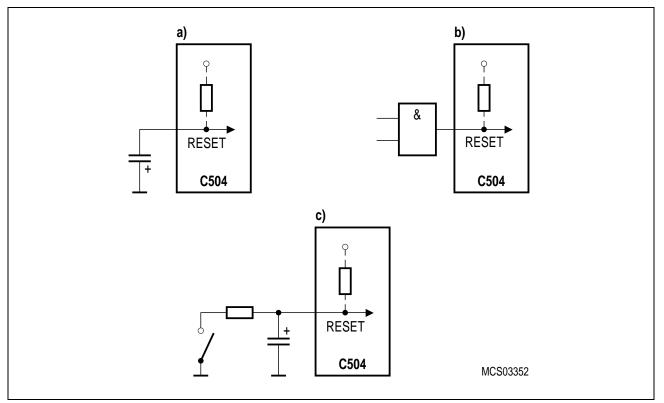

The reset input is an active high input. An internal Schmitt trigger is used at the input for noise rejection. Since the reset is synchronized internally, the RESET pin must be held high for at least two machine cycles (24 oscillator periods) while the oscillator is running.

During reset, pins ALE and PSEN are configured as inputs and should not be stimulated externally. (An external stimulation at these lines during reset activates several test modes which are reserved for test purposes. This, in turn, may cause unpredictable output operations at several port pins).

At the reset pin, a pulldown resistor is internally connected to  $V_{\rm SS}$  to allow a power-up reset with an external capacitor only. An automatic reset can be obtained when  $V_{\rm DD}$  is applied by connecting the reset pin to  $V_{\rm DD}$  via a capacitor. After  $V_{\rm DD}$  has been turned on, the capacitor must hold the voltage level at the reset pin for a specific time to effect a complete reset.

The time required for a reset operation is the oscillator start-up time and the time for 2 machine cycles, which must be at least 10 - 20 ms, under normal conditions. This requirement is typically met using a capacitor of 4.7 to 10  $\mu$ F. The same considerations apply if the reset signal is generated externally (**Figure 6b**). In each case, it must be assured that the oscillator has started up properly and that at least two machine cycles have passed before the reset signal goes inactive.

Figure 6 shows the possible reset circuitries.

Figure 6Reset Circuitries

**Figure 7** shows the recommended oscillator circuit for the C504, while **Figure 8** shows the circuit for using an external clock source.

#### Figure 7 Recommended Oscillator Circuit

#### **Enhanced Hooks Emulation Concept**

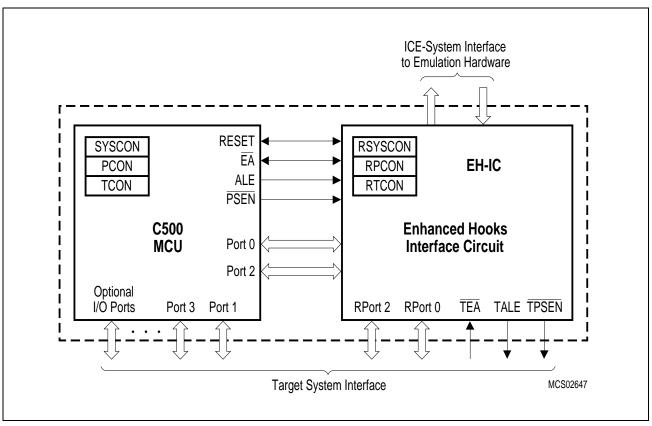

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative way to control the execution of C500 MCUs and to gain extensive information on the internal operation of the controllers. Emulation of on-chip ROM based programs is possible, too.

Each production chip has built-in logic for the support of the Enhanced Hooks Emulation Concept. Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation and production chips are identical.

The Enhanced Hooks Technology<sup>TM</sup>, which requires embedded logic in the C500 allows the C500 together with an EH-IC to function similar to a bond-out chip. This simplifies the design and reduces costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate all operating modes of the different versions of the C500. This includes emulation of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in single step mode and to read the SFRs after a break.

#### Figure 9 Basic C500 MCU Enhanced Hooks Concept Configuration

Port 0, Port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks Emulation Concept to control the operation of the device during emulation and to transfer informations about the program execution and data transfer between the external emulation hardware (ICE-system) and the C500 MCU.

#### **Special Function Registers**

All registers, except the program counter and the four general purpose register banks, reside in the special function register area.

The 63 special function registers (SFR) include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. All SFRs with addresses where address bits 0-2 are 0 (e.g.  $80_{H}$ ,  $88_{H}$ ,  $90_{H}$ ,  $98_{H}$ , ...,  $F0_{H}$ ,  $F8_{H}$ ) are bit-addressable.

The SFRs of the C504 are listed in **Table 2** and **Table 3**. In **Table 2**, they are organized in groups which refer to the functional blocks of the C504. **Table 3** illustrates the contents of the SFRs in numeric order of their addresses.

| Block               | Symbol                                                                             | Name                                                                                                                                                                                                                                      | Addr.                                                                                                                              | Contents<br>after<br>Reset                                                                                                                              |

|---------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                 | ACC<br>B<br>DPH<br>DPL<br>PSW<br>SP<br>SYSCON                                      | Accumulator<br>B-Register<br>Data Pointer, High Byte<br>Data Pointer, Low Byte<br>Program Status Word Register<br>Stack Pointer<br>System Control Register                                                                                | $\begin{array}{c} {\bf E0_{H}}^{1)} \\ {\bf F0_{H}}^{1)} \\ 83_{H} \\ 82_{H} \\ {\bf D0_{H}}^{1)} \\ 81_{H} \\ 81_{H} \end{array}$ |                                                                                                                                                         |

| Interrupt<br>System | IEN0<br>IEN1<br>CCIE <sup>2)</sup><br>IP0<br>IP1<br>ITCON                          | Interrupt Enable Register 0<br>Interrupt Enable Register 1<br>Capture/Compare Interrupt Enable Reg.<br>Interrupt Priority Register 0<br>Interrupt Priority Register 1<br>Interrupt Trigger Condition Register                             | $\begin{array}{c} \mathbf{A8_{H}}^{1)} \\ A9_{H} \\ D6_{H} \\ \mathbf{B8_{H}}^{1)} \\ B9_{H} \\ 9A_{H} \end{array}$                | $\begin{array}{c} 0 \\ 0 \\ X \\ 0 \\ 0 \\ 0 \\ 0 \\ X \\ 0 \\ 0 \\$                                                                                    |

| Ports               | P0<br>P1<br>P1ANA <sup>2)</sup><br>P2<br>P3<br>P3ANA <sup>2)</sup>                 | Port 0<br>Port 1<br>Port 1 Analog Input Selection Register<br>Port 2<br>Port 3<br>Port 3 Analog Input Selection Register                                                                                                                  | $80_{H}^{1}$ $90_{H}^{1}$ $90_{H}^{1)4}$ $A0_{H}^{1}$ $B0_{H}^{1)4}$                                                               | $ \begin{array}{c} FF_{H} \\ FF_{H} \\ XXXX1111_{B}^{3)} \\ FF_{H} \\ FF_{H} \\ FF_{H} \\ XX1111XX_{B}^{3)} \end{array} $                               |

| A/D-<br>Converter   | ADCON0<br>ADCON1<br>ADDATH<br>ADDATL<br>P1ANA <sup>2)</sup><br>P3ANA <sup>2)</sup> | A/D Converter Control Register 0<br>A/D Converter Control Register 1<br>A/D Converter Data Register High Byte<br>A/D Converter Data Register Low Byte<br>Port 1 Analog Input Selection Register<br>Port 3 Analog Input Selection Register |                                                                                                                                    | $\begin{array}{c} XX000000_{B}{}^{3)} \\ 01XXX000_{B}{}^{3)} \\ 00_{H} \\ 00XXXXXK_{B}{}^{3)} \\ XXX1111_{B}{}^{3)} \\ XX1111XX_{B}{}^{3)} \end{array}$ |

| Serial<br>Channels  | PCON <sup>2)</sup><br>SBUF<br>SCON                                                 | Power Control Register<br>Serial Channel Buffer Register<br>Serial Channel Control Register                                                                                                                                               | 87 <sub>H</sub><br>99 <sub>H</sub><br>98 <sub>H</sub> <sup>1)</sup>                                                                | 000X0000 <sub>B</sub><br>XX <sub>H</sub> <sup>3)</sup><br>00 <sub>H</sub>                                                                               |

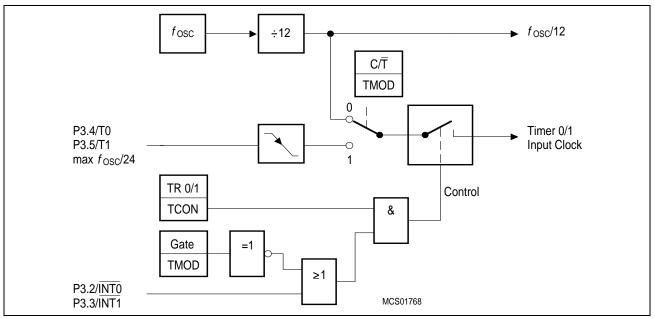

| Timer 0/<br>Timer 1 | TCON<br>TH0<br>TH1<br>TL0<br>TL1<br>TMOD                                           | Timer 0/1 Control Register<br>Timer 0, High Byte<br>Timer 1, High Byte<br>Timer 0, Low Byte<br>Timer 1, Low Byte<br>Timer Mode Register                                                                                                   | 88 <sub>H</sub> <sup>1)</sup><br>8C <sub>H</sub><br>8D <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>89 <sub>H</sub>       | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                                             |

#### Table 2 Special Function Registers - Functional Blocks

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) X means that the value is undefined and the location is reserved

| Table 2                      | Special Function Registers - Functional Blocks (cont'd)                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Block                        | Symbol                                                                                                                                                                                                                                             | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Addr.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Contents<br>after<br>Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Timer 2                      | T2CON<br>T2MOD<br>RC2H<br>RC2L<br>TH2<br>TL2                                                                                                                                                                                                       | Timer 2 Control Register<br>Timer 2 Mode Register<br>Timer 2 Reload Capture Register, High Byte<br>Timer 2 Reload Capture Register, Low Byte<br>Timer 2 High Byte<br>Timer 2 Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{c} \textbf{C8}_{\textbf{H}}^{1)} \\ \textbf{C9}_{\textbf{H}} \\ \textbf{CB}_{\textbf{H}} \\ \textbf{CA}_{\textbf{H}} \\ \textbf{CD}_{\textbf{H}} \\ \textbf{CD}_{\textbf{H}} \\ \textbf{CC}_{\textbf{H}} \end{array}$                                                                                                                                                                                                                                                                    | $\begin{array}{c} 00_{H} \\ XXXXXX0_{B}^{3)} \\ 00_{H} \\ 00_{H} \\ 00_{H} \\ 00_{H} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Capture /<br>Compare<br>Unit | CT1CON<br>CCPL<br>CCPH<br>CT1OFL<br>CT1OFH<br>CMSEL0<br>CMSEL1<br>COINI<br>TRCON<br>CCL0<br>CCH0<br>CCL0<br>CCH0<br>CCL1<br>CCH1<br>CCL2<br>CCH2<br>CCH2<br>CCH2<br>CCIR<br>CCIE <sup>2)</sup><br>CT2CON<br>CP2L<br>CP2H<br>CMP2L<br>CMP2H<br>BCON | Compare timer 1 control register<br>Compare timer 1 period register, low byte<br>Compare timer 1 offset register, high byte<br>Compare timer 1 offset register, high byte<br>Capture/compare mode select register 0<br>Capture/compare mode select register 1<br>Compare output initialization register<br>Trap enable control register<br>Capture/compare register 0, low byte<br>Capture/compare register 0, low byte<br>Capture/compare register 1, low byte<br>Capture/compare register 1, low byte<br>Capture/compare register 2, low byte<br>Capture/compare register 2, low byte<br>Capture/compare interrupt request flag reg.<br>Capture/compare interrupt enable register<br>Compare timer 2 period register, low byte<br>Compare timer 2 period register, low byte<br>Compare timer 2 compare register, high byte | $\begin{array}{c} {\sf E1}_{\sf H} \\ {\sf DE}_{\sf H} \\ {\sf DF}_{\sf H} \\ {\sf E6}_{\sf H} \\ {\sf E7}_{\sf H} \\ {\sf E3}_{\sf H} \\ {\sf E4}_{\sf H} \\ {\sf E2}_{\sf H} \\ {\sf C2}_{\sf H} \\ {\sf C2}_{\sf H} \\ {\sf C3}_{\sf H} \\ {\sf C3}_{\sf H} \\ {\sf C5}_{\sf H} \\ {\sf C6}_{\sf H} \\ {\sf D6}_{\sf H} \\ {\sf D2}_{\sf H} \\ {\sf D3}_{\sf H} \\ {\sf D5}_{\sf H} \\ {\sf D7}_{\sf H} \end{array}$ | $\begin{array}{c} 00010000_{B}\\ 00_{H}\\ 0$ |  |  |  |  |  |

| Watchdog<br>Timer            | WDCON<br>WDTREL                                                                                                                                                                                                                                    | Watchdog Timer Control Register<br>Watchdog Timer Reload Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>C0<sub>H</sub><sup>1)</sup></b><br>86 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XXXX0000 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Power<br>Saving<br>Mode      | PCON <sup>2)</sup><br>PCON1                                                                                                                                                                                                                        | Power Control Register<br>Power Control Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 87 <sub>H</sub><br>88 <sub>H</sub> <sup>1) 4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 000X0000 <sub>B</sub> <sup>3)</sup><br>0XXXXXX <sub>B</sub> <sup>3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

#### Table 2 Special Function Registers - Functional Blocks (cont'd)

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) X means that the value is undefined and the location is reserved

| Table 3                         |          |                                         |             |       |       |       |       |       |       |       |

|---------------------------------|----------|-----------------------------------------|-------------|-------|-------|-------|-------|-------|-------|-------|

| Addr                            | Register | Content<br>after<br>Reset <sup>1)</sup> | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 80 <sub>H</sub> <sup>2)</sup>   | P0       | FF <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 81 <sub>H</sub>                 | SP       | 07 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 82 <sub>H</sub>                 | DPL      | 00 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 83 <sub>H</sub>                 | DPH      | 00 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 86 <sub>H</sub>                 | WDTREL   | 00 <sub>H</sub>                         | WDT<br>PSEL | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 87 <sub>H</sub>                 | PCON     | 000X-<br>0000 <sub>B</sub>              | SMOD        | PDS   | IDLS  | -     | GF1   | GF0   | PDE   | IDLE  |

| 88 <sub>H</sub> <sup>2)</sup>   | TCON     | 00 <sub>H</sub>                         | TF1         | TR1   | TF0   | TR0   | IE1   | IT1   | IE0   | IT0   |

| 88 <sub>H</sub> <sup>1)3)</sup> | PCON1    | 0XXX-<br>XXXX <sub>B</sub>              | EWPD        | -     | -     | -     | -     | -     | -     | -     |

| 89 <sub>H</sub>                 | TMOD     | 00 <sub>H</sub>                         | GATE        | C/T   | M1    | MO    | GATE  | C/T   | M1    | M0    |

| 8A <sub>H</sub>                 | TL0      | 00 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 8B <sub>H</sub>                 | TL1      | 00 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 8C <sub>H</sub>                 | TH0      | 00 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 8D <sub>H</sub>                 | TH1      | 00 <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 90 <sub>H</sub> <sup>2)</sup>   | P1       | FF <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | T2EX  | T2    |

| 90 <sub>H</sub> <sup>2)3)</sup> | P1ANA    | XXXX-<br>1111 <sub>B</sub>              | _           | _     | -     | -     | EAN3  | EAN2  | EAN1  | EAN0  |

| 98 <sub>H</sub> <sup>2)</sup>   | SCON     | 00 <sub>H</sub>                         | SM0         | SM1   | SM2   | REN   | TB8   | RB8   | ТІ    | RI    |

| 99 <sub>H</sub>                 | SBUF     | ХХ <sub>Н</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| 9A <sub>H</sub>                 | ITCON    | 0010-<br>1010 <sub>B</sub>              | IT2         | IE2   | I2ETF | I2ETR | I1ETF | I1ETR | IOETF | I0ETR |

| A0 <sub>H</sub> <sup>2)</sup>   | P2       | FF <sub>H</sub>                         | .7          | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| A8 <sub>H</sub> <sup>2)</sup>   | IEN0     | 0X00-<br>0000 <sub>B</sub>              | EA          | -     | ET2   | ES    | ET1   | EX1   | ET0   | EX0   |

| A9 <sub>H</sub>                 | IEN1     | XX00-<br>0000 <sub>B</sub>              | _           | -     | ECT1  | ECCM  | ECT2  | ECEM  | EX2   | EADC  |

Table 3

Contents of the SFRs, SFRs in Numeric Order of their Addresses

1) X means that the value is undefined and the location is reserved

2) Bit-addressable special function registers